如何增加芯片中晶体管的数量来提高其速度?

Answers:

肯已经在回答中总结了一些原因。进一步扩展

- 更多缓存,比RAM快

显然,更大的缓存需要更多的晶体管。但是随着更多的晶体管,我们也可以选择使用更快的缓存。CPU缓存只是SRAM,通常由6个晶体管(AKA 6T SRAM)制成。但是,当有足够的晶体管时,可能值得使用更快但更大的,由6个以上晶体管组成的SRAM单元(例如8T,10T SRAM)

- 更多的SIMD指令,其处理速度比单数据指令快

不仅是SIMD,而且还有任何类型的加速指令。例如,现代体系结构通常具有用于更快地加密/解密的AES单元,用于更好的数学计算(尤其是数字信号处理)的FMA或用于更快的虚拟机的虚拟化。支持更多指令意味着需要更多资源来解码和执行它们

这些很清楚

过去,FPU没有足够的裸片面积,因此,如果对浮点运算有很高的要求,人们必须另外购买一个。有了更多的晶体管,就有可能内置FPU,从而大大加快了浮点运算的速度

此外,现代CPU是超标量的,即使指令流是线性和串行的,它们也会通过查找独立的数据并尽早计算来尝试同时完成多项任务。他们可以并行执行的操作越多,速度就会越快。为此,一个CPU可以具有多个ALU,而一个ALU可以具有多个执行单元。例如,如果一个CPU有5个加法器,而上一代则为4个,那么在最乐观的情况下,它的运行速度已经提高了25%,而没有任何时钟变化。更复杂的CPU甚至采用乱序执行(大多数现代高性能CPU就是这种情况)

- 更好的处理逻辑,例如更复杂的分支预测逻辑

操作通常可以以各种方式完成。如果您有更多的晶体管,您将有更多的资源来使用更快的技术。一些简单的例子:

移位:

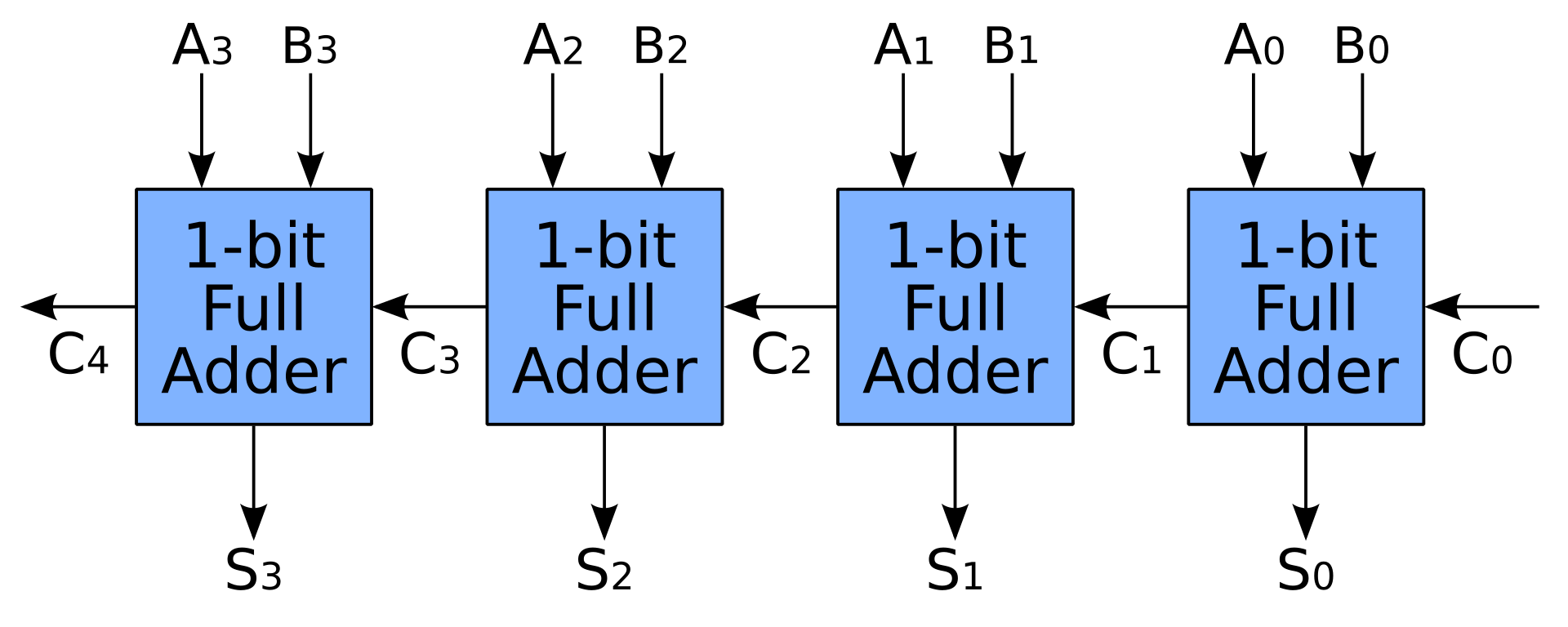

加成:

同样的事情也适用于其他单元,例如乘法器,除法器,调度器...例如,我们可以使用组合逻辑在单个时钟中极快地完成乘法。您可以在问题3位乘法器中看到一些简单的示例-它们如何工作?。但是所需的晶体管将增长到输入宽度的平方,因此带有乘法器的小型CPU使用顺序逻辑来节省大量的乘法器空间:

较老的乘法器体系结构使用移位器和累加器对每个部分积求和,通常每个周期一个部分积,将权衡速度换成芯片面积。现代乘法器体系结构使用(修改的)Baugh-Wooley算法,华莱士树或Dadda乘法器在单个周期中将部分乘积相加。通过修改Booth编码两个被乘数之一可以改善Wallace树实现的性能,从而减少了必须求和的部分乘积的数量。

一旦拥有大量晶体管,您甚至可以使用组合逻辑来进行FMA,这比乘法器要消耗更多的资源。

现代计算机可能包含专用MAC,该MAC由以组合逻辑实现的乘法器,加法器和存储结果的累加器寄存器组成。寄存器的输出被反馈到加法器的一个输入,以便在每个时钟周期,乘法器的输出被加到寄存器。组合乘法器需要大量的逻辑,但是比移位和加法早期计算机的典型方法要快得多。